一台 "桌面神器" 搞定 Nature成果?无掩膜直写光刻系统助力全功能2D NOR闪存芯片研发

发布日期:2025-12-12

近日,复旦大学周鹏、刘春森团队在二维电子学领域取得突破性进展,突破性成功研发出二维-硅基混合架构全功能 2D NOR 闪存芯片。该成果以 “A full-featured 2D flash chip enabled by system integration” 为题发表于《Nature》期刊,而小型台式无掩膜直写光刻系统- MicroWriter ML3在芯片核心电路模块加工中发挥关键支撑作用,这也是该设备助力发表的第7篇 Nature 正刊。

二维电子学应用转化的三大核心瓶颈

众所周知二维材料有着优异的电子性能(如高载流子迁移率、可调控能带结构)及范德华异质结特性,是国际上公认的成为突破硅基技术缩放极限的关键方向,尤其是在存储领域,二维闪存相比传统硅闪存,具备更快的福勒-诺德海姆(Fowler-Nordheim)隧穿编程速度和更优的通道长度缩放能力。

然而,2D电子学向系统级集成与实际应用转化仍面临三大核心瓶颈:1)2D与CMOS集成兼容性差:CMOS芯片表面经化学机械抛光后仍存在1-2 nm的粗糙度(远高于2D材料所需的<300pm平整基底),会导致2D材料产生随机应力和界面空隙,破坏其电学性能;2)片上工艺与封装难: 2D材料对电-热-机械(ETM)冲击极敏感,传统封装(高温键合、机械应力)易导致其性能退化甚至损坏;3)缺乏2D电路与CMOS模块的协同仿真-验证方法。

ATOM2CHIP 技术实现高效集成,MicroWriter ML3 提供关键工艺支撑

针对上述瓶颈,复旦大学周鹏、刘春森团队创新性提出原子器件到芯片(ATOM2CHIP)技术,通过“全栈片上工艺+跨平台系统设计”的双重创新,实现2D NOR闪存模块与CMOS平台的高效集成,最终制备出全功能2D NOR闪存芯片。

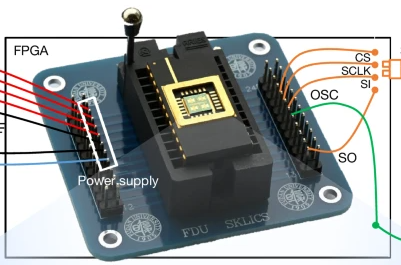

在该芯片的核心工艺环节,团队采用小型台式无掩膜直写光刻系统- MicroWriter ML3完成了关键加工任务,包括字线/位线/源线缓冲器、二硫化钼沟道、HfO₂/Pt/HfO₂存储堆叠的贯穿过孔等核心电路模块。

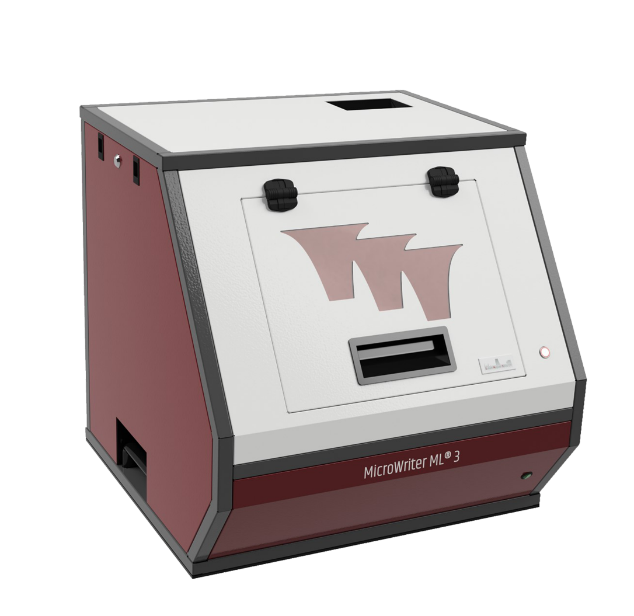

MicroWriter ML3 之所以成为该前沿研究的优选设备,得益于其四大核心优势:一是紧凑性,设备外观尺寸仅为70 cm X 70 cm X 70 cm,节省了实验空间;二是高精度,具备最高0.4 μm的加工分辨率,满足微纳尺度核心结构的加工要求;三是高效性,加工速度最高可达180 mm2/min,保障研发进程效率;四是稳定性,拥有极高的加工重现性,为实验数据的可靠性与芯片良率提供坚实保障。这些特性使其成为各个知名实验室微纳加工的必备设备。

小型台式无掩膜直写光刻系统- MicroWriter ML3

【精彩图文展示】

基于 ATOM2CHIP 技术的全功能二维闪存芯片

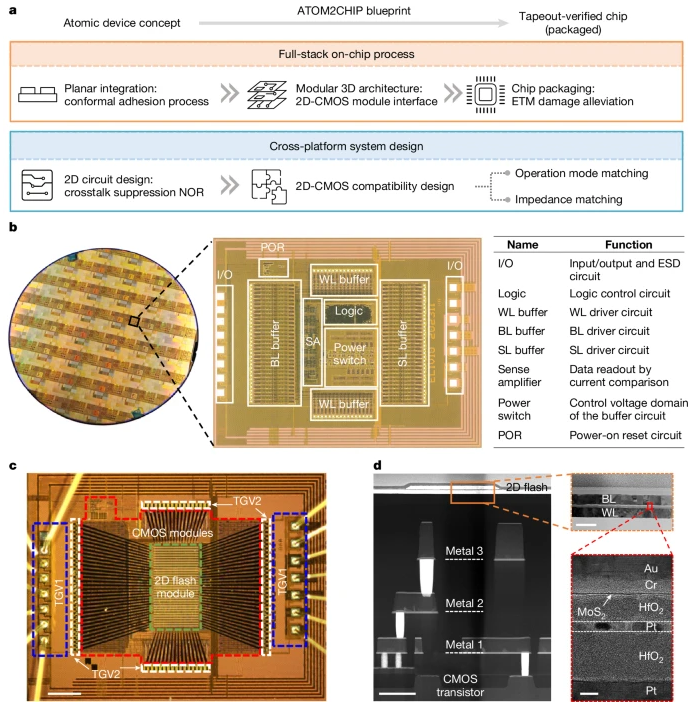

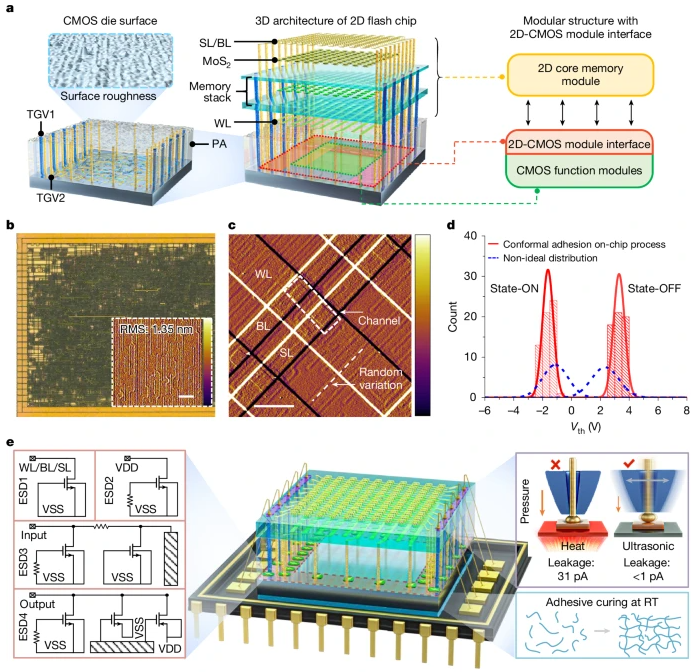

a. 基于 ATOM2CHIP 技术的技术蓝图,用于将原子级器件概念转化为通过流片验证的芯片。

b. 采用商用 0.13 微米技术节点制造的 CMOS 管芯。左图为包含所制造 CMOS 管芯的 8 英寸晶圆;中图为 CMOS 管芯的光学图像;右图为主要模块的功能说明。

c. 二维闪存芯片的光学图像。二维闪存模块集成于 CMOS 管芯上方,通过贯通玻璃孔TGVs实现连接。

d. 二维闪存芯片的扫描透射电镜(STEM)和高分辨透射电镜(HR-TEM)图像。STEM 图像证实了 CMOS 管芯与二维闪存模块的集成结构。HR-TEM 图像展示了二维闪存单元的逐级放大剖面。比例尺:c 图为 250 微米;d 图左为 1 微米;d 图右上为 200 纳米;d 图右下为 5 纳米。

全栈式片上工艺

a. 所制备二维闪存芯片的三维架构。左图:CMOS 管芯作为衬底,其上设有 800 纳米的钝化层(PA 层)用于隔离,以及用于信号传输的贯通玻璃孔(TGVs);右图:通过模块化设计将兼容性问题转化为二维 - CMOS 模块的接口设计问题。

b. CMOS 管芯的放大光学显微图像,突出展示了密集的随机电路布线。插图:对应的原子力显微镜(AFM)图像,均方根粗糙度(RMS)为 1.35 纳米(振幅范围 5 纳米)。

c. 集成于 CMOS 管芯上的二维闪存的 AFM 图像(振幅范围 8 纳米)。二维材料与粗糙 CMOS 管芯表面的共形附着有助于应力释放。

d. 二维闪存存储窗口表征的统计结果。通过共形附着片上工艺制备的二维闪存单元,其开关态阈值电压(Vth)分布紧凑且可区分(红色实线,数据取自扩展数据图 1a 中的 60 个单元);受良率和均匀性限制导致的非理想特性,表现为分布更宽且存在重叠(蓝色虚线)。

e. 二维友好型封装中综合保护方案的示意图。左图:分区静电放电(ESD)保护设计 ——ESD1 用于字线 / 位线 / 源极线(WL/BL/SL),ESD2 用于电源 / 地(VDD/VSS),ESD3 用于输入端,ESD4 用于输出端;阴影区域表示与对应焊盘相连的内部电路。右上:二维专用超声键合(右侧,低热预算、低应变)与传统热压键合(左侧,高热预算、高应变)的对比。右下:芯片贴装过程中的室温固化工艺。比例尺:b、c 图为 5 微米。

芯片核心性能与技术突破

全功能2D NOR闪存芯片基于ATOM2CHIP技术构建,通过全栈片上工艺(共形附着、模块化3D架构、2D友好封装),解决了2D材料在粗糙CMOS基底上的集成难题,实现94.34%的高良率; 2D闪存单元具备20 ns超快操作速度与0.644pJ/bit低能耗,芯片支持32位并行、指令驱动与随机访问,满足系统级应用需求;创新性建立“2D器件-CMOS平台”的协同集成框架,为2D电子学向实际应用转化提供了可复用的技术范式。